توضیحات

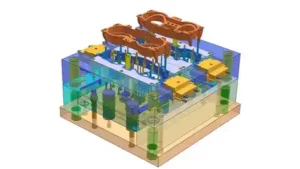

پیادهسازی الگوریتمهای محاسباتی سنگین بر روی سیستم های تعبیه شده

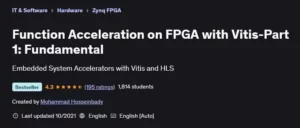

نام دوره : Function Acceleration on FPGA with Vitis-Part 1: Fundamental

پیش نیاز:

- درک مفاهیم پایهای کدنویسی C/C++

- نرمافزار پلتفرم یکپارچه Xilinx Vitis

- یک FPGA مبتنی بر Zynq مانند Zybo-Z7-20 یا Ultra96v2

توضیحات

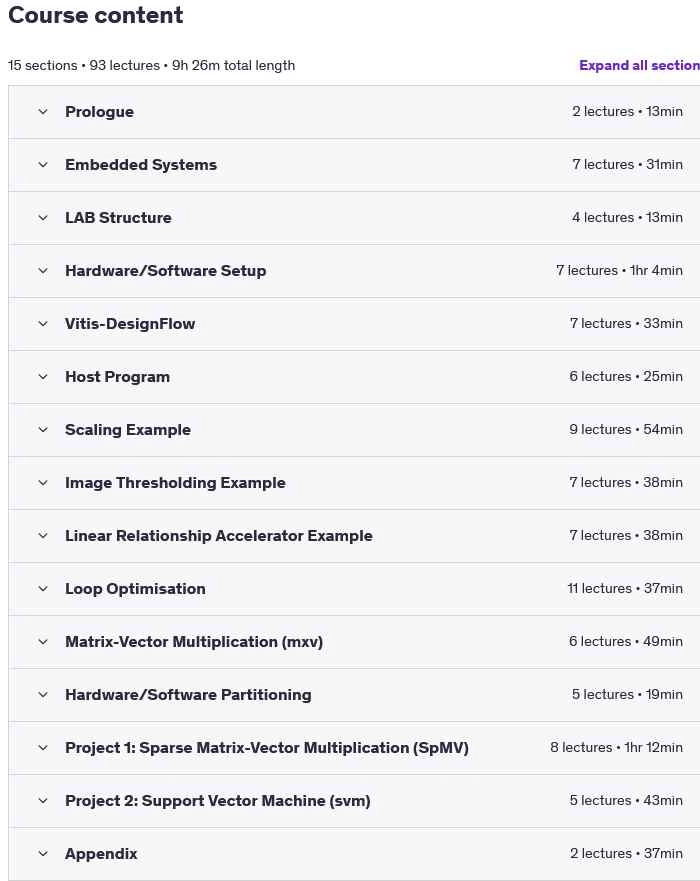

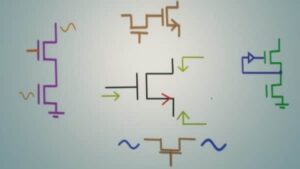

این دوره مقدمهای است بر شتابدهی عملکرد در سنتز سطح بالا (HLS).

اهداف دوره شامل توضیح، اشکالزدایی و پیادهسازی الگوریتمهای محاسباتی سنگین بر روی سیستمهای جاسازی شده مبتنی بر FPGA با استفاده از زبان C/C++ بدون نیاز به HDLs (مانند VHDL یا Verilog) است.

دوره به معرفی سیستمهای جاسازی شده Xilinx Zynq پرداخته و سپس توضیح میدهد که چگونه از مجموعه ابزارهای Xilinx برای نقشهبرداری برنامهها روی این سیستمها استفاده کنیم.

این دوره از پلتفرم نرمافزاری یکپارچه Xilinx Vitis برای توضیح مثالها و کاربردهای واقعی سیستمهای جاسازی شده استفاده میکند. دوره از روشهای شبیهسازی نرمافزاری و سختافزاری پیروی میکند و برنامهها را روی FPGAهای واقعی اجرا میکند.

هر بخش از دوره پیادهسازی الگوریتمهای محاسباتی سنگین بر روی سیستم های تعبیه شده از چندین مثال، آزمونها و تمرینها برای توضیح مفاهیم پیچیده طراحی به روشی ساده و روان استفاده میکند.

در طول دوره، شما با چندین مثال کار خواهید کرد که مفاهیم و تکنیکهای HLS را توضیح میدهند. این دوره شامل تعداد زیادی آزمون و تمرین است تا شما بتوانید روشها و رویکردهای مطرح شده را تمرین کرده و تسلط پیدا کنید. علاوه بر این، دوره از دو پروژه جذاب استفاده میکند تا تمام مفاهیم توضیح داده شده را برای طراحی مدارها و کنترلرهای سختافزاری واقعی به هم متصل کند.

این دوره اولین دوره از مجموعه دورههای شتابدهی عملکرد بر روی سیستمهای جاسازی شده مبتنی بر Zynq است. در حالی که این دوره بر مفاهیم بنیادی تمرکز دارد، دورههای دیگر تکنیکهای بهینهسازی مختلف در Vitis را توضیح خواهند داد.

دوره پیادهسازی الگوریتمهای محاسباتی سنگین بر روی سیستم های تعبیه شده برای چه کسانی است:

- مهندسین سختافزار

- مهندسین نرمافزار که به FPGA علاقهمند هستند

- مدرسین، محققان، و اساتیدی که میخواهند از سیستمهای جاسازی شده مبتنی بر FPGA در دروس، دورهها یا تحقیقات خود استفاده کنند

یودمی ایران –

دوره درخواستی خود را از راه های ارتباطی درخواست کنید