توضیحات

تایید صحت سخت افزار با SystemVerilog قسمت دوم: پروژه ها

نام دوره : SystemVerilog for Verification Part 2 : Projects

پیش نیاز:

- مبانی Verilog، الکترونیک دیجیتال

دوره زیر به عنوان پیش نیاز دوره پیشنهاد می شود:

توضیحات:

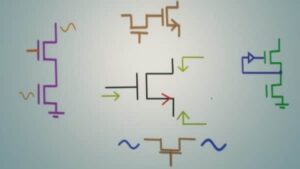

صنعت VLSI را می توان به دو شاخه تقسیم کرد، یعنی طراحی RTL و تأیید RTL. Verilog و VHDL انتخاب های محبوب برای اکثر مهندسان طراحی که در طراحی RTL کار می کنند باقی می مانند.

تأیید عملکردی را میتوان با زبان توصیف سختافزار نیز انجام داد، اما زبان توصیف سختافزار قابلیتهای محدودی برای انجام تحلیل پوشش کد، تست گوشهای و غیره دارد و نوشتن کد TB ممکن است برای سیستمهای پیچیده گاهی غیرممکن باشد.

SystemVerilog به انتخاب اصلی مهندسان تأیید برای انجام تأیید صحت RTLهای پیچیده تبدیل شده است.

قابلیت های شی گرا SystemVerilog مانند وراثت، پلی مورفیسم و تصادفی سازی به کاربران اجازه می دهد تا باگ های مهم را با حداقل تلاش پیدا کنند.

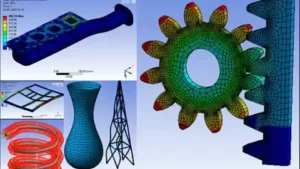

هر سیستم پیچیده در FPGA ها با کمک زیرسیستم های متعدد ساخته می شود. این زیرسیستم ها می توانند اجزای متوالی ساده / اجزای ترکیبی ساده / پروتکل های ارتباطی داده RTL / پروتکل اتوبوس RTL باشند.

هنگامی که استراتژیهای انجام تأیید سیستمهای فرعی رایج را فهمیدیم، میتوانید به راحتی هر سیستم پیچیده را با همان منطق تأیید کنید.

هدف ما برای این دوره، ایجاد منطق با کمک اصولی که در قسمت اول دوره مورد بحث قرار گرفت، برای انجام راستیآزمایی این زیرسیستمهای رایج خواهد بود.

دوره تایید صحت سخت افزار با SystemVerilog قسمت دوم: پروژه ها با انجام راستیآزمایی فلیپ فلاپهای داده و FIFO شروع میکنیم، سپس به تأیید پروتکلهای رایج ارتباط داده، یعنی SPI، UART و I2C میپردازیم.

در نهایت، ما تأیید پروتکل های گذرگاه، یعنی پروتکل ABP، AHB، AXI و Whishbone را انجام خواهیم داد.

دوره تایید صحت سخت افزار با SystemVerilog قسمت دوم: پروژه ها برای چه کسانی است:

- هر کسی که مایل به یادگیری تأیید RTL با SystemVerilog است

یودمی ایران –

دوره درخواستی خود را از راه های ارتباطی درخواست کنید