توضیحات

آموزش پیاده سازی AXI4 در طراحی FPGA

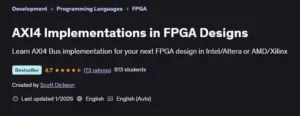

نام دوره : AXI4 Implementations in FPGA Designs

پیش نیاز:

مقداری تجربه با شبیهسازهای رفتاری میتواند مفید باشد.

توضیحات

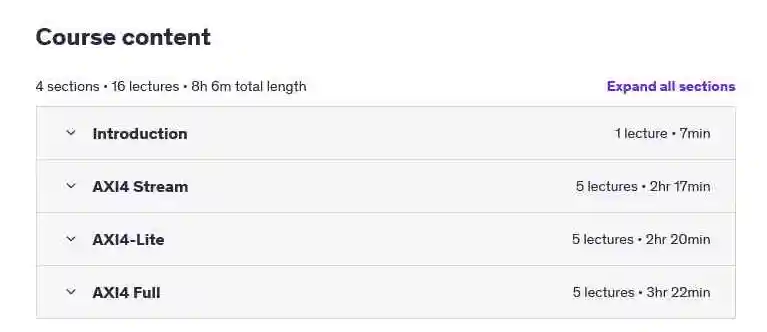

یک مجموعه آموزشی کامل در مورد تمام جنبههای پروتکل باس AXI4، شامل AXI4 Stream، AXI4-Lite و AXI4.

هر نوع از AXI4 شامل جریان داده، مکانیزم هندشیک (handshake)، و الزامات سیگنالی است که بهصورت دقیق توضیح داده شدهاند.

پیادهسازی نمونهای از Master و Slave برای هرکدام از زیرمجموعههای AXI4 نیز ارائه شده است، همراه با نمایش شبیهسازی با استفاده از testbenchهای نمونه در edaplayground و Vivado، و استفاده از دیاگرام بلوکی Vivado با بررسی پروتکل AXI4.

ما تفاوتهای بین انواع AXI4 را بررسی میکنیم.

پروتکل AXI4 Stream برای انتقال حجم بالای دادهها بهصورت یکطرفه از master به slave بدون استفاده از آدرسدهی کاربرد دارد.

این پروتکل سادهترین نوع AXI4 برای پیادهسازی است و بیشترین کاربرد را دارد.

پروتکل AXI4-Lite نیز یکی دیگر از رابطهای رایج است که نحوه پیادهسازی آن را فرا میگیریم.

بهطور کامل درک خواهیم کرد که چگونه master در AXI4-Lite با slave از طریق ارسال آدرس و داده تبادل میکند و عملیات نوشتن و خواندن تککلمهای را انجام میدهد، و پاسخهای معتبر یا خطا از سوی slave دریافت میشود.

پروتکل کامل AXI4 بالاترین پهنای باند داده را ارائه میدهد، با حالت burst تا ۲۵۶ کلمه با اندازه ۱۲۸ بایت.

این پروتکل شامل ۵ باس جداگانه است: باس نوشتن آدرس، باس نوشتن داده، باس خواندن آدرس، باس خواندن داده، و باس پاسخ نوشتن — که هرکدام مکانیزم هندشیک مجزایی دارند. بنابراین برای پیادهسازی موفق این کامپوننتها در سطح RTL، نیاز به درک عمیق و دقیق از پروتکل وجود دارد.

دوره آموزش پیاده سازی AXI4 در طراحی FPGA برای چه کسانی مناسب است:

طراحان منطق FPGA

طراحان نرمافزارهای تعبیهشده مبتنی بر FPGA

یودمی ایران –

دوره درخواستی خود را از راه های ارتباطی درخواست کنید