توضیحات

آموزش پیاده سازی مدارهای منطقی ترکیبی بر روی FPGA با زبان سی پلاس پلاس

نام دوره : High-Level Synthesis for FPGA, Part 1-Combinational Circuits

پیش نیاز:

- درک مفاهیم پایهای کدنویسی C/C++

- درک مفاهیم پایهای عملگرهای منطقی (مانند AND، OR، XOR، SHIFT)

- برد ارزیابی BASYS3

- نرمافزارهای Xilinx Vitis-HLS و Vivado (نسخه Vivado ML Edition یا Vivado Design Suite – HLx Editions را برای ویندوز یا لینوکس دانلود کنید)

توضیحات

دوره آموزش پیاده سازی مدارهای منطقی ترکیبی بر روی FPGA با زبان سی پلاس پلاس یک معرفی ابتدایی به جریان طراحی synthesis سطح بالا (HLS) است.

اهداف این دوره شامل توصیف، اشکالزدایی و پیادهسازی مدارهای منطقی ترکیبی بر روی FPGA با استفاده از زبانهای C/C++ بدون هیچگونه کمک از HDLها (مانند VHDL یا Verilog) است.

HLS اخیراً توسط برخی از رهبران صنعتی (مانند Nvidia و Google) برای طراحی پلتفرمهای سختافزار و نرمافزار خود مورد استفاده قرار گرفته است.

جریان طراحی HLS آینده طراحی سختافزار است که به سرعت به یک مهارت ضروری برای هر مهندس سختافزار یا نرمافزار که به دنبال استفاده از FPGA برای عملکرد فوقالعاده و مصرف پایین انرژی آن است تبدیل میشود.

این دوره از نرمافزار و پلتفرمهای سختافزاری Xilinx HLS برای نمایش مثالها و برنامههای واقعی استفاده میکند.

این دوره اولین دورهای است که جریان طراحی HLS و مهارتها را همراه با مفاهیم مدارهای منطقی دیجیتال از ابتدا میسازد.

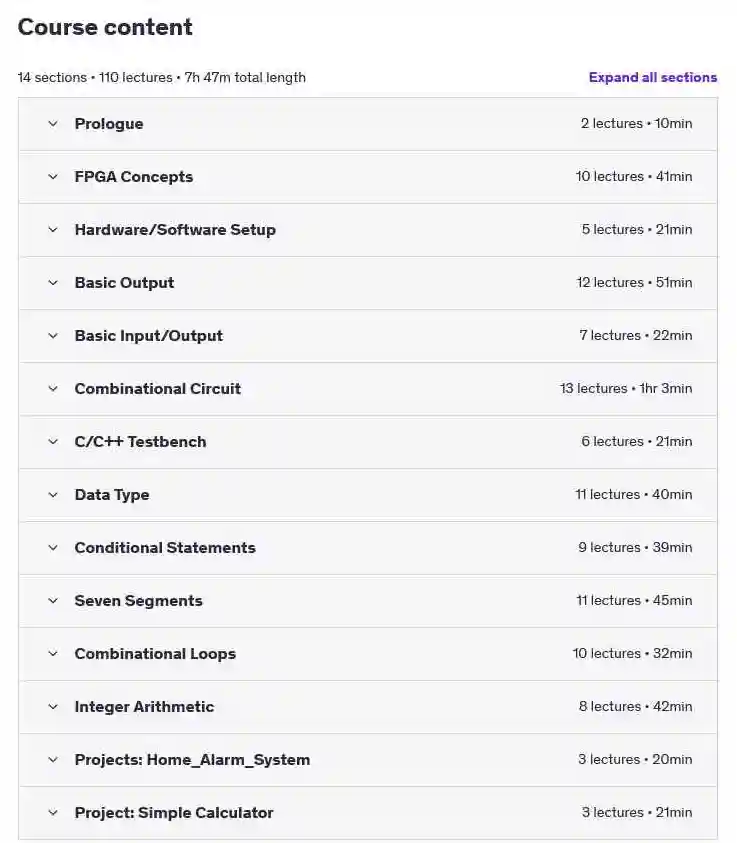

در طول دوره، شما با مثالهای مختلفی آشنا میشوید که مفاهیم و تکنیکهای HLS را توضیح میدهند.

این دوره شامل آزمونها و تمرینهای متعدد است که به شما کمک میکند تا روشها و رویکردهای پیشنهادی را تمرین و تسلط پیدا کنید.

این دوره اولین دوره از یک سری دورهها درباره HLS در طراحی ماژولهای سختافزاری و تسریع الگوریتمها روی FPGA هدف است.

در حالی که این دوره بر مدارهای ترکیبی تمرکز دارد، دورههای دیگر در این سری توضیح میدهند که چگونه از HLS در طراحی مدارهای منطقی ترتیبی، تسریع الگوریتمها و سیستمهای ترکیبی CPU+ FPGA استفاده کنیم.

دوره آموزش پیاده سازی مدارهای منطقی ترکیبی بر روی FPGA با زبان سی پلاس پلاس برای چه کسانی است:

مهندسان سختافزار

مهندسان نرمافزاری که به FPGA علاقهمند هستند

اساتید، محققان، استادان دانشگاه که میخواهند از HLS مبتنی بر FPGA در دروس، دورهها یا تحقیقهای خود استفاده کنند

علاقهمندان به مدارهای منطقی دیجیتال

یودمی ایران –

دوره درخواستی خود را از راه های ارتباطی درخواست کنید